This page has links to all the documentaton resourcesavailable for Yosys.

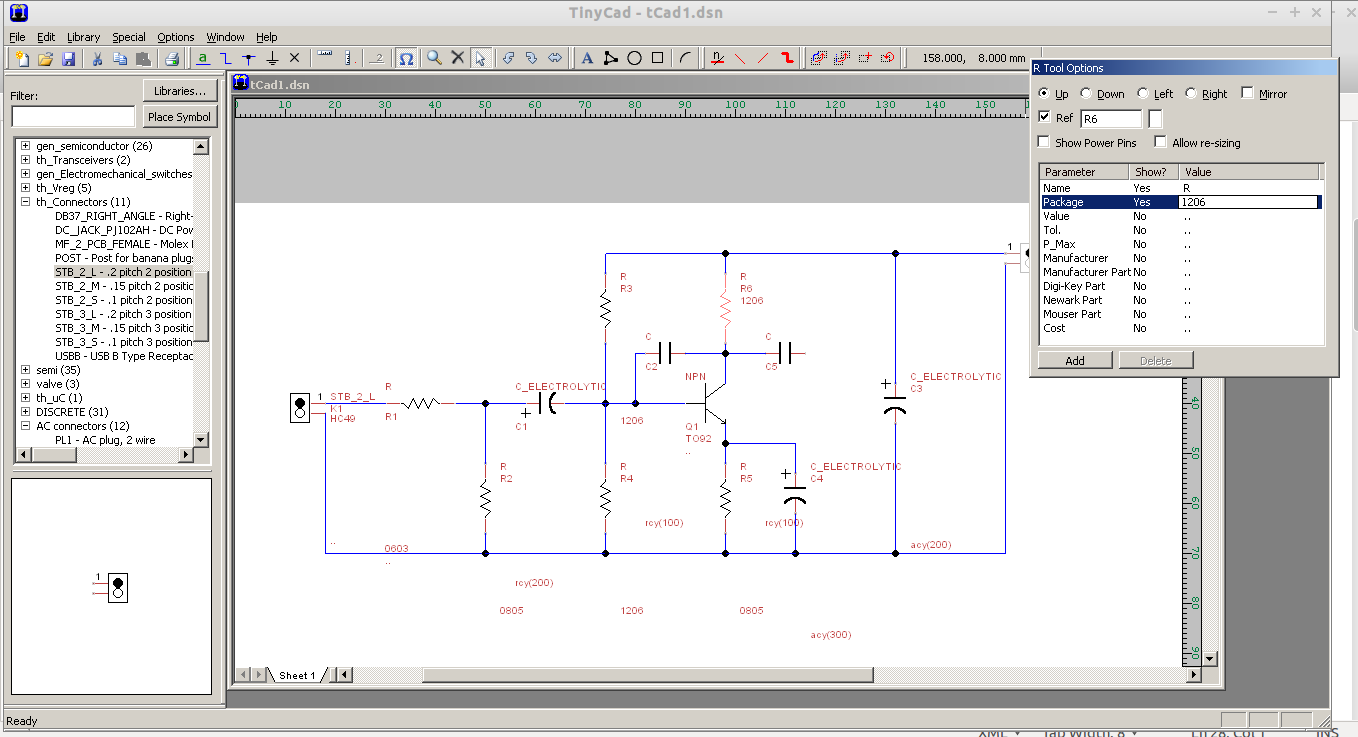

EDIF (Electronic Design Interchange Format) is a vendor neutral format in which to store Electronic netlists and schematics. It was one of the first attempts to establish a data exchange format for the electronic design automation (EDA) industry. The goal was to establish a common format from which the proprietary formats of the EDA systems could be derived.

- Generating PartMiner edaXML-Format Files for Use with Other EDA Tools; Generating Board-Level Signal Integrity Analysis Files. Generating HSPICE Simulation Deck Files for External Signal Integrity Analysis; Generating Boundary-Scan Description Language Files. Create Board-Level Boundary-Scan File Window (File Menu) Using Project Revisions.

- Electronic Data Interchange Format file. An industry standard file format for specifying a design netlist.

Yosys Manual

A quick first-steps tutorial can be found in the README file.

The Yosys manual can be downloaded here (PDF).

What Is A Netlist

Support

The best places to ask questions are the Yosys Subreddit, Stack Overflow and#yosys on freenode.The best place to report a bug is on GitHub.

Presentation Slides

This presentation slides cover a wide range of topics related to Yosys. (The LaTeX source is part of the Yosys source distribution. Fell free to adapt the slides as needed.)

Application Notes

Papers and other Publications

- Clifford Wolf, Johann Glaser. Yosys - A Free Verilog Synthesis Suite.In Proceedings of Austrochip 2013.[download pdf]

- Johann Glaser and Clifford Wolf. Methodology and Example-Driven InterconnectSynthesis for Designing Heterogeneous Coarse-Grain ReconfigurableArchitectures. In Jan Haase, editor, Models, Methods, and Tools forComplex Chip Design. Lecture Notes in Electrical Engineering. Volume 265,2014, pp 201-221. Springer, 2013.[download pdf]

Command Reference

- abcuse ABC for technology mapping

- addadd objects to the design

- aigmapmap logic to and-inverter-graph circuit

- alumaccextract ALU and MACC cells

- anlogic_determine_initAnlogic: Determine the init value of cells

- anlogic_eqnAnlogic: Calculate equations for luts

- assertpmuxadds asserts for parallel muxes

- async2syncconvert async FF inputs to sync circuits

- attrmaprenaming attributes

- attrmvcpmove or copy attributes from wires to driving cells

- blackboxconvert modules into blackbox modules

- bugpointminimize testcases

- cda shortcut for 'select -module <name>'

- checkcheck for obvious problems in the design

- chformalchange formal constraints of the design

- chparamre-evaluate modules with new parameters

- chtypechange type of cells in the design

- cleanremove unused cells and wires

- clk2fflogicconvert clocked FFs to generic $ff cells

- connectcreate or remove connections

- connwrappersmatch width of input-output port pairs

- coolrunner2_sopbreak $sop cells into ANDTERM/ORTERM cells

- copycopy modules in the design

- coverprint code coverage counters

- cutpointadds formal cut points to the design

- debugrun command with debug log messages enabled

- deletedelete objects in the design

- deminoutdemote inout ports to input or output

- designsave, restore and reset current design

- determine_initDetermine the init value of cells

- dff2dffetransform $dff cells to $dffe cells

- dff2dffsprocess sync set/reset with SR over CE priority

- dffinitset INIT param on FF cells

- dfflibmaptechnology mapping of flip-flops

- dffsr2dffconvert DFFSR cells to simpler FF cell types

- dumpprint parts of the design in ilang format

- echoturning echoing back of commands on and off

- ecp5_ffinitECP5: handle FF init values

- edgetypeslist all types of edges in selection

- equiv_addadd a $equiv cell

- equiv_inductproving $equiv cells using temporal induction

- equiv_makeprepare a circuit for equivalence checking

- equiv_markmark equivalence checking regions

- equiv_miterextract miter from equiv circuit

- equiv_optprove equivalence for optimized circuit

- equiv_purgepurge equivalence checking module

- equiv_removeremove $equiv cells

- equiv_simpletry proving simple $equiv instances

- equiv_statusprint status of equivalent checking module

- equiv_structstructural equivalence checking

- evalevaluate the circuit given an input

- exposeconvert internal signals to module ports

- extractfind subcircuits and replace them with cells

- extract_counterExtract GreenPak4 counter cells

- extract_fafind and extract full/half adders

- extract_reduceconverts gate chains into $reduce_* cells

- flattenflatten design

- flowmappack LUTs with FlowMap

- fmcombinecombine two instances of a cell into one

- freduceperform functional reduction

- fsmextract and optimize finite state machines

- fsm_detectfinding FSMs in design

- fsm_expandexpand FSM cells by merging logic into it

- fsm_exportexporting FSMs to KISS2 files

- fsm_extractextracting FSMs in design

- fsm_infoprint information on finite state machines

- fsm_mapmapping FSMs to basic logic

- fsm_optoptimize finite state machines

- fsm_recoderecoding finite state machines

- greenpak4_dffinvmerge greenpak4 inverters and DFF/latches

- helpdisplay help messages

- hierarchycheck, expand and clean up design hierarchy

- hilomaptechnology mapping of constant hi- and/or lo-drivers

- historyshow last interactive commands

- ice40_braminitiCE40: perform SB_RAM40_4K initialization from file

- ice40_dspiCE40: map multipliers

- ice40_ffinitiCE40: handle FF init values

- ice40_ffssriCE40: merge synchronous set/reset into FF cells

- ice40_optiCE40: perform simple optimizations

- ice40_unlutiCE40: transform SB_LUT4 cells to $lut cells

- insbufinsert buffer cells for connected wires

- iopadmaptechnology mapping of i/o pads (or buffers)

- jsonwrite design in JSON format

- logprint text and log files

- lslist modules or objects in modules

- ltpprint longest topological path

- lut2muxconvert $lut to $_MUX_

- maccmapmapping macc cells

- memorytranslate memories to basic cells

- memory_brammap memories to block rams

- memory_collectcreating multi-port memory cells

- memory_dffmerge input/output DFFs into memories

- memory_maptranslate multiport memories to basic cells

- memory_memxemulate vlog sim behavior for mem ports

- memory_nordffextract read port FFs from memories

- memory_shareconsolidate memory ports

- memory_unpackunpack multi-port memory cells

- miterautomatically create a miter circuit

- mutategenerate or apply design mutations

- muxcovercover trees of MUX cells with wider MUXes

- muxpack$mux/$pmux cascades to $pmux

- nlutmapmap to LUTs of different sizes

- onehotoptimize $eq cells for onehot signals

- optperform simple optimizations

- opt_cleanremove unused cells and wires

- opt_demorganOptimize reductions with DeMorgan equivalents

- opt_exprperform const folding and simple expression rewriting

- opt_lutoptimize LUT cells

- opt_mergeconsolidate identical cells

- opt_muxtreeeliminate dead trees in multiplexer trees

- opt_reducesimplify large MUXes and AND/OR gates

- opt_rmdffremove DFFs with constant inputs

- peepoptcollection of peephole optimizers

- pluginload and list loaded plugins

- pmux2shiftxtransform $pmux cells to $shiftx cells

- pmuxtreetransform $pmux cells to trees of $mux cells

- prepgeneric synthesis script

- proctranslate processes to netlists

- proc_arstdetect asynchronous resets

- proc_cleanremove empty parts of processes

- proc_dffextract flip-flops from processes

- proc_dlatchextract latches from processes

- proc_initconvert initial block to init attributes

- proc_muxconvert decision trees to multiplexers

- proc_rmdeadeliminate dead trees in decision trees

- qwpquadratic wirelength placer

- readload HDL designs

- read_aigerread AIGER file

- read_blifread BLIF file

- read_ilangread modules from ilang file

- read_jsonread JSON file

- read_libertyread cells from liberty file

- read_verilogread modules from Verilog file

- renamerename object in the design

- rmportsremove module ports with no connections

- satsolve a SAT problem in the circuit

- scatteradd additional intermediate nets

- sccdetect strongly connected components (logic loops)

- scriptexecute commands from script file

- selectmodify and view the list of selected objects

- setattrset/unset attributes on objects

- setparamset/unset parameters on objects

- setundefreplace undef values with defined constants

- sf2_iobsSF2: insert IO buffers

- shareperform sat-based resource sharing

- shellenter interactive command mode

- showgenerate schematics using graphviz

- shregmapmap shift registers

- simsimulate the circuit

- simplemapmapping simple coarse-grain cells

- splicecreate explicit splicing cells

- splitnetssplit up multi-bit nets

- statprint some statistics

- submodmoving part of a module to a new submodule

- supercoveradd hi/lo cover cells for each wire bit

- synthgeneric synthesis script

- synth_achronixsynthesis for Acrhonix Speedster22i FPGAs.

- synth_anlogicsynthesis for Anlogic FPGAs

- synth_coolrunner2synthesis for Xilinx Coolrunner-II CPLDs

- synth_easicsynthesis for eASIC platform

- synth_ecp5synthesis for ECP5 FPGAs

- synth_gowinsynthesis for Gowin FPGAs

- synth_greenpak4synthesis for GreenPAK4 FPGAs

- synth_ice40synthesis for iCE40 FPGAs

- synth_intelsynthesis for Intel (Altera) FPGAs.

- synth_sf2synthesis for SmartFusion2 and IGLOO2 FPGAs

- synth_xilinxsynthesis for Xilinx FPGAs

- tclexecute a TCL script file

- techmapgeneric technology mapper

- teeredirect command output to file

- test_abcloopautomatically test handling of loops in abc command

- test_autotbgenerate simple test benches

- test_cellautomatically test the implementation of a cell type

- torderprint cells in topological order

- traceredirect command output to file

- tribufinfer tri-state buffers

- uniquifycreate unique copies of modules

- verificload Verilog and VHDL designs using Verific

- verilog_defaultsset default options for read_verilog

- verilog_definesdefine and undefine verilog defines

- wbflipflip the whitebox attribute

- wreducereduce the word size of operations if possible

- write_aigerwrite design to AIGER file

- write_blifwrite design to BLIF file

- write_btorwrite design to BTOR file

- write_edifwrite design to EDIF netlist file

- write_filewrite a text to a file

- write_firrtlwrite design to a FIRRTL file

- write_ilangwrite design to ilang file

- write_intersynthwrite design to InterSynth netlist file

- write_jsonwrite design to a JSON file

- write_simplecconvert design to simple C code

- write_smt2write design to SMT-LIBv2 file

- write_smvwrite design to SMV file

- write_spicewrite design to SPICE netlist file

- write_tablewrite design as connectivity table

- write_verilogwrite design to Verilog file

- zinitadd inverters so all FF are zero-initialized

EDIF Input File (.edf) |

An EDIF version 2 0 0 netlist file (with the extension (.edf), generated by any standard EDIF netlist writer. The Quartus II software also supports EDIF Input files with the extensions (.edif) or (.edn).

When you compile an EDIF Input File, the Compiler uses one or more Library Mapping Files (.lmf) to map cells in an EDIF Input File to corresponding Quartus II logic functions, including Library of Parameterized Modules (LPM) functions, as well as to user-defined functions.

All logic functions in an EDIF Input File must be mapped to the Quartus II software logic functions in a Library Mapping File (.lmf). If you wish to use a function that is not mapped in a Altera-provided LMF, you must create a customized LMF. You can map EDIF cells to Altera-provided functions or to any design file created with the Quartus II software.

Netlist Format

The Compiler processes EDIF Input Files automatically, generating a Compiler Netlist Extractor (. cnf) file for every cell in an EDIF Input File. You can also specify EDIF Input settings to help the Compiler interpret EDIF Input Files by specifying optional LMFs and non-default VCC and GND signal names.

Edif File Format

A single EDIF Input File can be used to define all logic in a project, or can be incorporated at any hierarchy level in a hierarchical project.

The Quartus II software automatically creates a Block Symbol File (.bsf) that represents an EDIF Input File when you open the file in the Text Editor and create the default symbol for the current file. This symbol and the logic it represents can be incorporated into a Block Design File (.bdf).

You can also use EDIF Input File logic in an AHDL Text Design File (.tdf) by including a Function Prototype and inserting an instance of the function into the TDF.

You can import some resource assignments into the Quartus II software with the following EDIF property constructs:

Construct: | Type of Assignment: |

chip_pin_lc | Chip, pin, logic cell |

clique | clique |

logic_option | Logic option |

As an alternative, you can use the Assignment Editor in the Quartus II software to make all types of assignments--including location and device assignments--for the logic in the EDIF Input File.

To properly convert an EDIF Input File, EDIF constructs must have the following values:

Construct: | Value: |

edifLevel | 0 |

keywordLevel | 0 |

viewType | NETLIST |

cellType | GENERIC |

The file name may be truncated to 8 characters. If you truncate the file name, you must then either rename the file with its previous longer file name from within the Quartus II software, or edit the file to change any instances of the file name to the new, truncated name. To rename the file from within the Quartus II software, open the file with the truncated name in the Text Editor and save it to its previous longer file name. However, if your file transfer software inserts characters into the truncated name that are not legal Quartus II software name characters, you may need to first rename the file from the DOS command line before you can open it in the Text Editor.